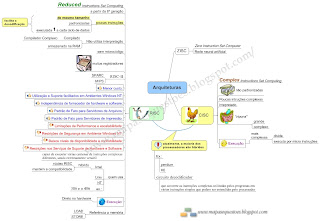

Estou tentando seguir o programa da maioria dos concurso de TI. Então, mais um pouco de Arquitetura de Computadores.

Agora um assunto muito recorrente: RISC X CISC.

A maior parte dos comentário desse mapa foi tirado de questões de prova.

------------------------------------------------

Na Arquitetura RISC,

a) as instruções geradas pelos compiladores são armazenadas na memória ROM e para serem executadas na CPU devem ser inicialmente interpretadas pelos microprogramas.

b) as instruções são interpretadas por microprogramas e posteriormente armazenadas na CPU.

c) as instruções, na sua maioria, necessitam de mais de um ciclo de máquina para serem executadas.

d) o código gerado pelos compiladores é constituído de instruções complexas, armazenados na memória EPROM.

e) as instruções geradas pelos compiladores são armazenadas na memória RAM.

Comentários:

Esse assunto não é muito forte, mas vamos lá.

a) Risc não usa interpretação.

b) idem 'a'

c) Tinha marcado essa, pois como são ciclos reduzidos, achei que teria que ter ciclos. Exemplo: para 2 x 3, teria q fazer 2 + 2 + 2. Mas está errado.

d) instruções Complexa são CISC

e) resposta certa

Gab.: E

------------------------------------------------------

Mais mapas mentias consulte

www.mapasequestoes.com.br

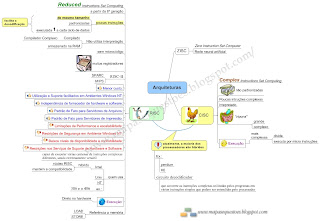

Estou tentando seguir o programa da maioria dos concurso de TI. Então, mais um pouco de Arquitetura de Computadores.

Agora um assunto muito recorrente: RISC X CISC.

A maior parte dos comentário desse mapa foi tirado de questões de prova.

------------------------------------------------

Na Arquitetura RISC,

a) as instruções geradas pelos compiladores são armazenadas na memória ROM e para serem executadas na CPU devem ser inicialmente interpretadas pelos microprogramas.

b) as instruções são interpretadas por microprogramas e posteriormente armazenadas na CPU.

c) as instruções, na sua maioria, necessitam de mais de um ciclo de máquina para serem executadas.

d) o código gerado pelos compiladores é constituído de instruções complexas, armazenados na memória EPROM.

e) as instruções geradas pelos compiladores são armazenadas na memória RAM.

Comentários:

Esse assunto não é muito forte, mas vamos lá.

a) Risc não usa interpretação.

b) idem 'a'

c) Tinha marcado essa, pois como são ciclos reduzidos, achei que teria que ter ciclos. Exemplo: para 2 x 3, teria q fazer 2 + 2 + 2. Mas está errado.

d) instruções Complexa são CISC

e) resposta certa

Gab.: E

------------------------------------------------------

Mais mapas mentias consulte www.mapasequestoes.com.br

Estou tentando seguir o programa da maioria dos concurso de TI. Então, mais um pouco de Arquitetura de Computadores.

Agora um assunto muito recorrente: RISC X CISC.

A maior parte dos comentário desse mapa foi tirado de questões de prova.

------------------------------------------------

Na Arquitetura RISC,

a) as instruções geradas pelos compiladores são armazenadas na memória ROM e para serem executadas na CPU devem ser inicialmente interpretadas pelos microprogramas.

b) as instruções são interpretadas por microprogramas e posteriormente armazenadas na CPU.

c) as instruções, na sua maioria, necessitam de mais de um ciclo de máquina para serem executadas.

d) o código gerado pelos compiladores é constituído de instruções complexas, armazenados na memória EPROM.

e) as instruções geradas pelos compiladores são armazenadas na memória RAM.

Comentários:

Esse assunto não é muito forte, mas vamos lá.

a) Risc não usa interpretação.

b) idem 'a'

c) Tinha marcado essa, pois como são ciclos reduzidos, achei que teria que ter ciclos. Exemplo: para 2 x 3, teria q fazer 2 + 2 + 2. Mas está errado.

d) instruções Complexa são CISC

e) resposta certa

Gab.: E

------------------------------------------------------

Mais mapas mentias consulte www.mapasequestoes.com.br